晶振輸出邏輯對頻率有什么影響,又怎樣盡可能降低抖動?

晶振輸出邏輯對頻率有什么影響,又怎樣盡可能降低抖動?

輸出邏輯是Oscillator所特有的屬性,其表示晶振頻率信號輸出之后會以什么樣的波形呈現(xiàn);輸出邏輯通常有兩種模式,一種是單端輸出一種是差分輸出,其中輸出包含正弦輸出和削頂正弦輸出以及方波輸出,而差分輸出的話一般就是差分晶振所用,但是目前已經(jīng)出現(xiàn)一些在SPXO有源晶振也會掛載;那么晶振的輸出邏輯對頻率有什么影響呢,使用什么樣的輸出方式可盡可能的降低抖動呢?

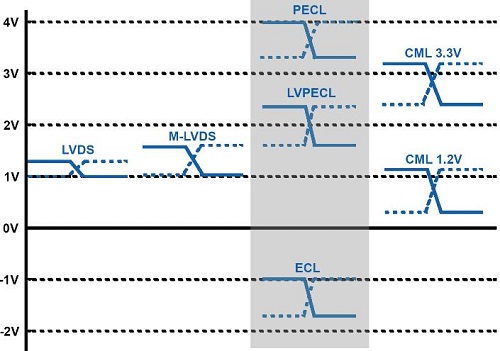

想要達到這樣的目的,那么就必須要對各種輸出邏輯有一定認識和理解;而振蕩器的輸出邏輯大概有11種,這里我們就不一一列舉了,就挑其中幾種較為常見的來說明一下.

首先是CMOS,HCMOS以及LVCMOS;CMOS,HCMOS和LVCMOS都屬于互補金屬氧化物半導體類別.它們是最適合低頻時鐘(通常低于250MHz)的方波數(shù)字輸出.這允許在時鐘輸出和芯片輸入之間直接連接.在大多數(shù)情況下,可以使用低值串聯(lián)電阻器來有效減少信號反饋并保持可靠的信號完整性.

其次是正弦波和削頂正弦波,正弦波-是晶體或石英晶體振蕩器電路的標準或”自然”信號輸出.它由一個基本正弦頻率輸出組成.線性正弦波輸出可在所有輸出中提供最佳的相位噪聲性能.這些非常適合需要高質(zhì)量輸出信號的應用.削波正弦波-正弦波輸出受到控制,因此不會達到其最大高電平或低電平.這樣,您將創(chuàng)建一個方波輸出,而不會犧牲任何所需的相位噪聲性能.

再就是LVPECL,LVPECL為千兆位以太網(wǎng)和光纖通道的使用奠定了良好的基礎(chǔ).LVPECL就像LVDS在電氣上一樣,但提供更大的差分電壓擺幅和稍低的電源效率.LVPECL的輸出可能會帶來挑戰(zhàn),因為需要端接來發(fā)射電壓.同樣,芯片中的差分電路可能具有不同的輸入容差.確保檢查是否正確端接以達到最佳性能.

最后就是LVDS了,LVDS類似于LVPECL輸出,但是LVDS的功耗較低,并且電壓擺幅較小.LVDS通常用于滿足時鐘分配或背板收發(fā)器等高速數(shù)據(jù)傳輸需求.為了獲得更高的數(shù)據(jù)速率,通常首選HCSL,CML或LVPECL,但與LVDS相比,其功耗更高.其他好處包括降低了對噪聲的敏感性,并且易于在CMOSIC中實現(xiàn).

但是LVDS有明顯的缺點,那就是是與PECL相比,其抖動性能降低,但是正在尋求新技術(shù)以實現(xiàn)與LVPECL相同水平的抖動性能.

一般來說,如果要得到更低的抖動性能,會采用LVPECL,LVDS,CMOS這三種輸出方式;但是根據(jù)上述來看,很明顯使用LVDS的石英晶振抖動性能比LVPECL要差一些,它表現(xiàn)出的優(yōu)越性能是功耗低,所以這種輸出更適合于用在需要降低功耗的產(chǎn)品上.但是出去另外兩者之外它又是最適合的地抖動振蕩器的.

晶振輸出邏輯對頻率有什么影響,又怎樣盡可能降低抖動?

“推薦閱讀”

相關(guān)技術(shù)支持

- Pletronics低功耗SM2245KE-32.768K-T3K晶體振蕩器的精度和功率效率

- ACT艾西迪SY00003GIHD‐PF晶體術(shù)語的A到Z技術(shù)論文

- CRYSTEK振蕩器CCPD-575X-20-80.000晶體負載計算

- LV-PECL石英晶振,LV-LVDS晶振,LV-PECL振蕩器,LVDS-HCSL普通有源晶振貼片四腳/而差分有源晶振則是貼片六腳

- 泰藝開發(fā)的壓控溫補振蕩器VC-TCXO,適合用于手機TXEADCSANF-26.000000

- Abracon晶振開發(fā)AX5系列的有源振蕩器AX5PAF1-26.00000,支持差分輸出

- 晶振輸出邏輯對頻率有什么影響,又怎樣盡可能降低抖動?

- 為什么晶振會出現(xiàn)頻偏,用什么方法可以最大化縮小其影響

- 鎖相環(huán)設(shè)計中的VCXO Oscillator性能權(quán)衡

- SMD與DIP封裝的石英振蕩器規(guī)格應用