用于拓撲結(jié)構(gòu)的皮爾斯門振蕩器負載計算

用于拓撲結(jié)構(gòu)的皮爾斯門振蕩器負載計算

晶振數(shù)據(jù)表中的參數(shù)由負載電容是中心頻率的容差或校準在25°C如果振蕩器電路的設(shè)計不匹配負載電容值,那么中心頻率不會在數(shù)據(jù)表的容差限制,有趣的是,一個所謂的并聯(lián)晶體要求其有效串聯(lián)電容負載與其終端,因為晶體是無源元件,所以石英晶體振蕩器電路丟失了,是的振蕩器電路設(shè)計者或芯片的責任制造商指定晶體可能具有的最大損失確保在所有條件下可靠啟動,那么皮爾斯門振蕩器是給水晶呈現(xiàn)了什么?

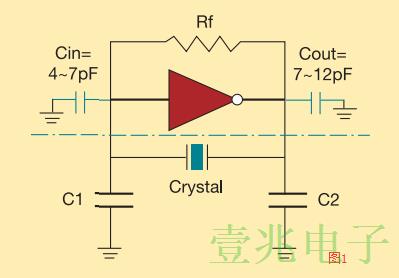

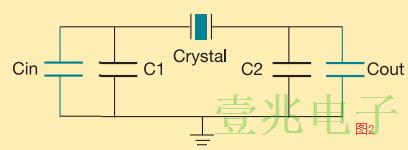

了解如何正確指定石英晶體,用于拓撲結(jié)構(gòu)的晶體圖1可以是基本AT-CUT或BT-CUT,BT-CUT晶體很差與AT-CUT相比,溫度下的頻率穩(wěn)定性,此拓撲使用a平行晶體而非串聯(lián)晶體,當指定平行晶體時,晶體因此,制造商想要一個負載電容,要了解負載電容,可以考慮串聯(lián)LC電路晶體諧振器是L,電容是C.聲音LC電路的頻率希望隨L和C的變化而變化,但是在晶體情況下,L是固定的(溫度不是參數(shù)).大多數(shù)晶振廠家忽視的圖2中最重要的事實是逆變器門的內(nèi)部輸入和輸出電容,論文與外部(C1和C2)相比具有重要價值,如果Cin并且沒有指定Cout,那么每個的猜測值為5pF是好的開始.

可以通過改變啟動過程來優(yōu)化電路C1和C2的值,所以不要丟掉你的主要寬容,計算你的振蕩器容性負載,現(xiàn)在你知道如何計算負載能力了電路呈現(xiàn)給石英晶體,你應(yīng)該選擇什么負載電容?在回答之前這個問題,你需要知道晶體中心頻率的靈敏度負載電容,這被稱為修剪靈敏度S.其中Cm是晶體的運動電容,Co是晶體的并聯(lián)電容,andload是負載電容.

從修剪靈敏度中可以看出,Cload越小,越大修剪靈敏度,換句話說,如果你正在設(shè)計固定頻率時鐘,那么你選擇高的Cload值,如20pF,但是,如果您正在設(shè)計可變頻率VCXO振蕩器,選擇低Cload值搜索為14 pF,因此,C1和C2值會影響振蕩器的增益,值越低,越高收益,同樣,C2/ C1比率也會影響增益,要增加增益,請使C1小于C2.

最常見的皮爾斯門振蕩器今天使用到目前為止是穿孔門,它的受歡迎程度源于這樣一個事實數(shù)字逆變器通常是包含在微處理器中,簡單的分析就足夠了傳達皮爾斯門的關(guān)鍵點石英振蕩器操作,大多數(shù)設(shè)計師都很熟悉使用皮爾斯門振蕩器,但很少有人真正理解如何它的功能,更不用說如何了正確設(shè)計它作為一種常見的練習,大多數(shù)甚至不付錢過分關(guān)注振蕩器在他們的設(shè)計中,直到它不起作用正確的,通常已經(jīng)釋放到生產(chǎn),情況并非如此.

“推薦閱讀”

- 采用尖端硅技術(shù)的新型振蕩器SSO32C3A481-25.000M是6G模塊的理想選擇

- HCMOS表面貼裝晶體振蕩器ECS-3225MVLC非常適合物聯(lián)網(wǎng)應(yīng)用

- 以太網(wǎng)交換機常用的晶振SG7050CCN編碼X1G004501005700

- 醫(yī)療設(shè)備應(yīng)用晶振SG5032CAN編碼X1G004451000300

- 低功耗藍牙智能燈控制模塊晶振X1G005231000400

- X1G005421020400愛普生溫補晶振TCXO溫度補償方式石英晶體振蕩器的應(yīng)用

- TXC科技發(fā)布的進口晶振TE微機電系統(tǒng)振蕩器,BF-125.000MBE-T,有源晶振

- 超微型四腳型的高質(zhì)量晶體諧振器FW2000008,超級適合用于手持電腦,ECERA品牌

- ASVV-52.000MHZ-C25-N102-T壓控晶振是Abracon專為精密GPS,基站應(yīng)用設(shè)計的產(chǎn)品

- 石英晶體振蕩器使用注意事項

相關(guān)技術(shù)支持

- Pletronics低功耗SM2245KE-32.768K-T3K晶體振蕩器的精度和功率效率

- ACT艾西迪SY00003GIHD‐PF晶體術(shù)語的A到Z技術(shù)論文

- CRYSTEK振蕩器CCPD-575X-20-80.000晶體負載計算

- LV-PECL石英晶振,LV-LVDS晶振,LV-PECL振蕩器,LVDS-HCSL普通有源晶振貼片四腳/而差分有源晶振則是貼片六腳

- 泰藝開發(fā)的壓控溫補振蕩器VC-TCXO,適合用于手機TXEADCSANF-26.000000

- Abracon晶振開發(fā)AX5系列的有源振蕩器AX5PAF1-26.00000,支持差分輸出

- 晶振輸出邏輯對頻率有什么影響,又怎樣盡可能降低抖動?

- 為什么晶振會出現(xiàn)頻偏,用什么方法可以最大化縮小其影響

- 鎖相環(huán)設(shè)計中的VCXO Oscillator性能權(quán)衡

- SMD與DIP封裝的石英振蕩器規(guī)格應(yīng)用